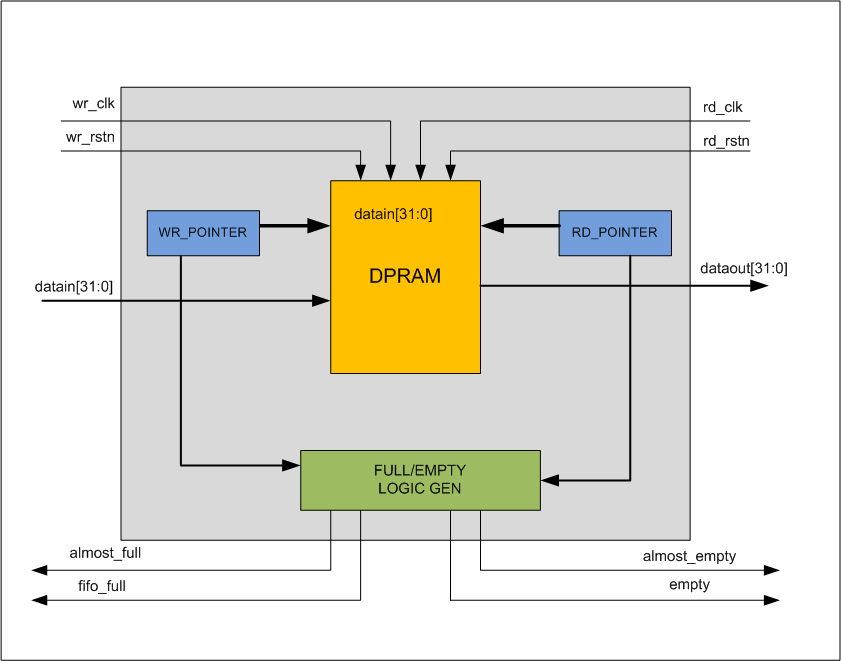

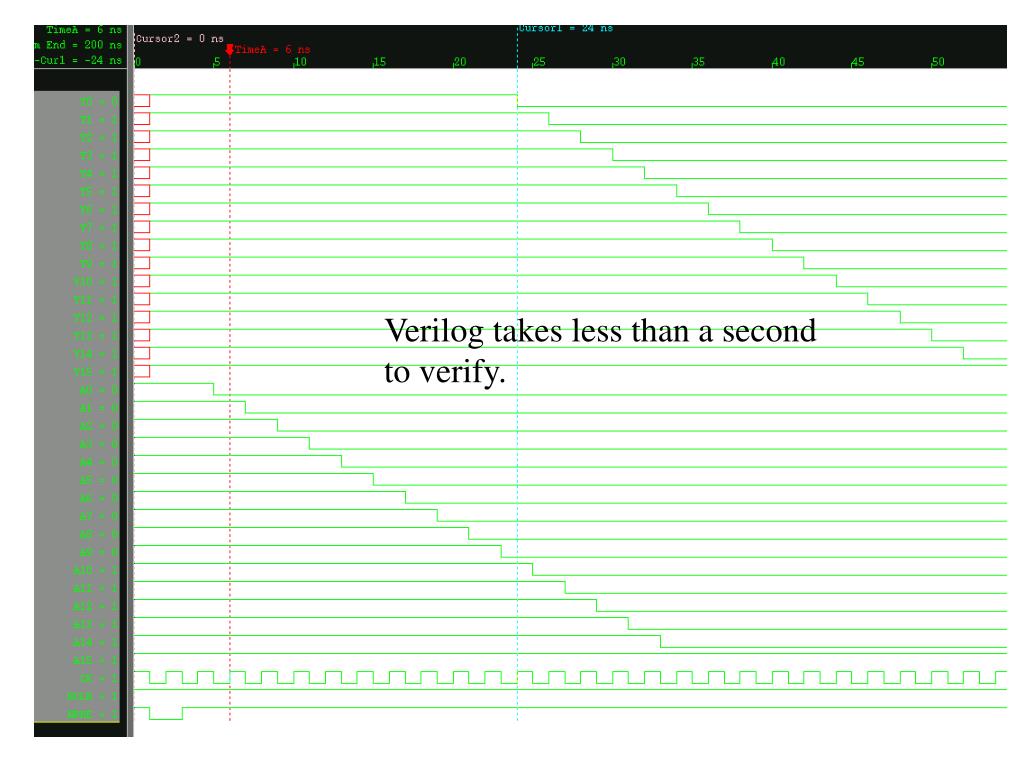

The below diagram shows the load and extract operations and the impact of them on the full and empty signals The full indication will remain asserted in that case. Simultaneous load and extract operations to the FIFO when full indication is asserted will result is a write of the datain to the FIFO and a read to the dataout. The load and extract operations of the FIFO impact the FIFO pointers. When the load signal is asserted, the data on the datain is loaded into the position pointed by the write pointer and the pointer is then incremented by 1 to point to the next FIFO entry. If the FIFO full indication is asserted, and the extract signal is not asserted, the load operation would be ignored and the pointer would not be incremented. The FIFO depth and width are parameters that can be set to any valid value at instantiation. Additional parameter sets the width of the required address of the FIFO i.e., for a FIFO of depth 16, 4 bits would be required.īasic flop based FIFO should be used only for relatively small arrays where timing requirement can be met, for bigger arrays, a memory based FIFO should be used. For that reason, the typical application would mask the load signal with the full indication, preventing the simultaneous load and extract while the FIFO is full.

When the FIFO is full, simultaneous load and extract is supported, but care must be taken as the upstream logic has no indication whether the data has been loaded or dropped without evaluating the extract signal. The status indications are implemented using a wrap-around bit in the pointers. The FIFO reset functionality is either synchronous or asynchronous and should be used according to the overall reset policy of the instantiating device. The generic synchronous FIFO for log2 depths is designed with a flip-flop memory array and a set of read pointer and write pointer. Load operations are ignored while FIFO is full Extract operations are ignored while FIFO is empty Indicates a FIFO entry is to be read, will be ignored when FIFO is empty Indicates the FIFO is to be written, will be ignored when FIFO is full and extract is de-asserted

Active low reset signal, when asserted, pointers would return to zero and empty indication would be set

0 kommentar(er)

0 kommentar(er)